中山大学微电子学院官众副教授带领的EDA算法研究团队,联合澳门大学、珠海芯聚科技有限公司(Chipoly),在ArXiv平台接连发布了《Fusing Global and Local: Transformer-CNN Synergy for Next-Gen Current Estimation》(https://arxiv.org/pdf/2504.07996与《S-Crescendo: A Nested Transformer Weaving Framework for Scalable Nonlinear System in S-Domain Representation》(https://arxiv.org/pdf/2505.11843) 等研究论文。

该研究工作首次将Transformer架构成功应用于数字电路后端签核(Signoff)领域,通过创新算法设计,实现了数字电路信号线RC波形仿真,在保持SPICE级精度的同时,将效率提升数十倍,攻克了高精度与高效率难以兼得的技术难题。

官众副教授指出,该研究工作的重要意义在于:将传统签核EDA软件中的计算仿真问题转换成了学习回归问题,快速精准预测信号线的RC电流响应,为数字电路后端三大签核(时序、功耗、可靠性)提供了共用的核心参数(即标准单元信号线路径电学仿真结果),也为未来统一后端三大电学签核引擎奠定了理论基础。

后摩尔时代的签核面临严峻挑战:

在后摩尔时代,半导体工艺已经出现了两条清晰的发展路线:一方面晶圆制造厂商继续向物理极限缩小晶体管尺寸,以达到单晶片性能的增加和功耗的减少,而这会导致芯片上晶体管密度和功耗密度的上升,而且每一层金属导线也会变得更细,更密集;另一方面是通过采用先进封装技术来实现芯片性能和集成度提升的阵营,比如2.5D/3D/Chiplet封装,不同种类的晶片堆叠在一起,虽然单晶片设计已经比较成熟,但将很多异构晶片堆叠封装在一起会带来很多新问题,例如芯片过热的问题。这些新技术的出现使得确保芯片设计有效的签核工具面临严峻挑战:

1、效率瓶颈:精准的SPICE仿真依赖牛顿迭代法求解非线性方程,效率低下,已淡出数字后端签核。

2、精度局限:7nm以下工艺,主流商业工具(如新思PrimeTime、RedHawk)采用CCS和RC等效模型,功耗和可靠性指标(平均电流、均方根电流、峰值电流)计算误差可高达15%[1]。

3、流程割裂:时序、功耗、压降及电迁移等签核环节相互独立,无法考虑耦合效应,增加设计迭代成本。

官众团队提出的创新解决方案:

中山大学官众团队聚焦EDA底层算法创新,此次突破针对数字电路特性重新设计了算法架构,而非简单移植AI模型。

1. 电路建模革新:以标准单元(standard cell)为基本单元,将RC电路网表和传递函数转化为矩阵形式的token序列,构建Transformer可识别的电路拓扑表达。

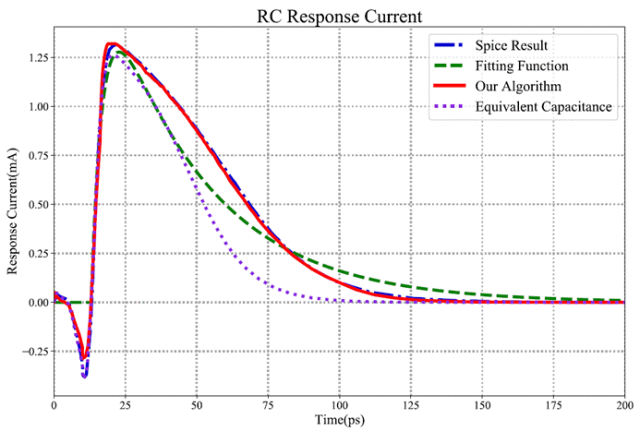

2. 回归算法替代:摒弃传统微分方程迭代求解,通过深度学习直接预测电流波形、信号延时等关键指标,效率较SPICE提升10-20倍以上。

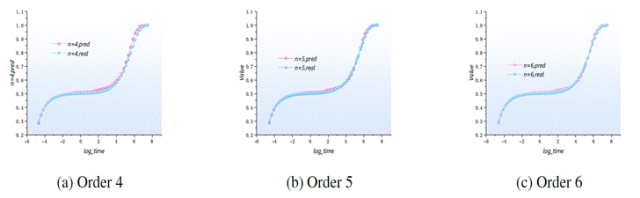

3. 高维泛化推广:少量低维矩阵训练即可覆盖海量高维电路场景,单工艺节点内预测误差稳定在0.5%以内。

该项成果的显著优势与核心竞争力:

1、精度高:波形预测与SPICE结果重合度达99.9%,延时计算误差<0.5%。

2、速度快:典型14nm工艺电路全路径时序及功耗仿真耗时从数小时缩短至几分钟,有望将千亿级晶体管芯片的后端签核周期从数月压缩至数周。

3、泛用性强:单次训练模型可支持工艺节点内不同设计版图,取代传统的K库-lib-RC抽取-PT冗长流程。

4、拓展性好:可为Chiplet、3D等先进封装技术提供仿真支持。

加速推进EDA工具链的国产替代:

官众博士表示,该成果有望加速国产EDA工具链替代进程,突破海外技术壁垒。他强调国产EDA签核工具的瓶颈已从与Foundry的合作迭代转变成了AI模型的嵌入应用,并指出“国产签核工具完成替代之时,就是国产芯片产业链崛起之时”。

目前,已有多家芯片设计公司正与中山大学及芯聚科技开展合作对接。这项来自中国高校与企业的原创性成果,正通过“产学研”(中山大学微电子学院官众副教授带领的EDA算法研究团队、澳门大学、珠海芯聚科技有限公司)的深度合作,为全球半导体行业提供新的技术选择,期许改写行业规则与格局。

Reference

[1]. Zhoujie Wu et al., “A Dynamic Capacitance Matching (DCM)-Based Current Response Algorithm for Signal Line RC Network”IEEE Transactions on Circuits and Systems I: Regular Papers, Volume: 71, Issue: 12, December 2024, Page(s): 5804 - 5813, DOI: 10.1109/TCSI.2024.3463708